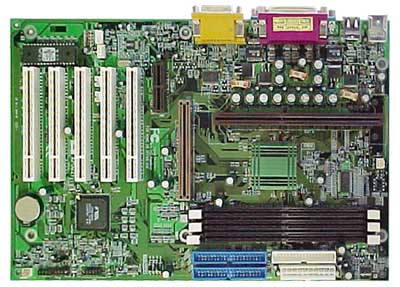

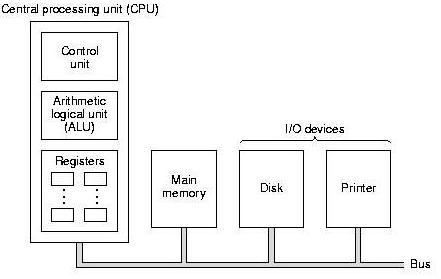

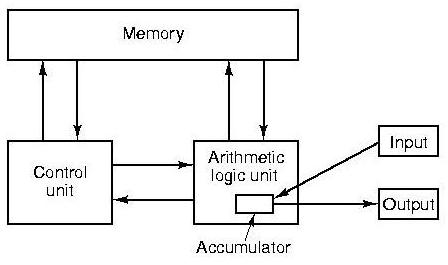

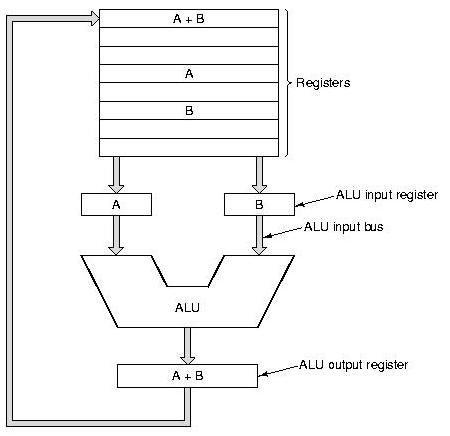

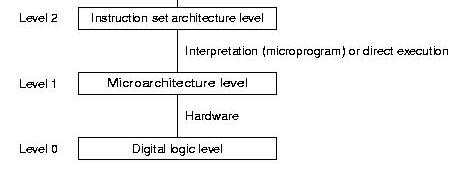

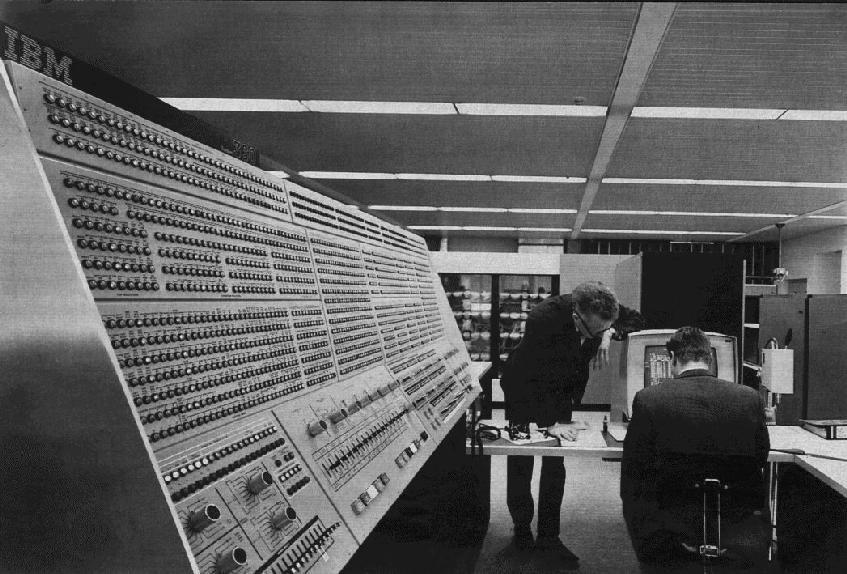

- Processors - CPU Organization, instruction, execution, RISC vs. CISC, design principles, paralellism

- Primary Memory - Bits, addresses, byte ordering, error-correcting codes, cache, memory packaging and types

- Secondary Memory - memory hierarchies, magnetic disks, floopy disks, IDE, SCSI, RAID, CD-ROM, CD-R, CD-RW, DVD

- Input/Output - buses, terminals, mice, printers, modems, character codes.

>

>